선릉역 1번 출구

컴퓨터 구조(5) - CPU의 속도 본문

클럭

- 컴퓨터 부품들은 '클럭 신호'에 맞춰 움직임

- CPU는 명령어 사이클에 맞춰 명령어를 실행함

클럭 신호가 빠름 -> 컴퓨터 부품들이 빠르게 움직임 -> CPU가 명령어 사이클을 더 빠르게 반복함

결론: 클럭 속도가 빠르면 일반적으로 CPU가 성능이 좋지만 속도만 높인다고해서 성능이 계속 좋아지지는 않음(발열 문제)

클럭 속도: 헤르츠(Hz) - 1초에 클럭이 몇 번 반복되는지를 나타냄

*속도가 일정한 것이 아니라 기본 클럭 속도(Base)와 최대 클럭 속도(Max)로 나뉨, 고성능을 요하는 순간에는 순간적으로 클럭 속도를 높임

+오버클럭킹: 최대 클럭 속도를 강제로 끌어 올리는 것

코어 and 멀티 코어

명령어를 실행하는 부품 = Core

과거의 CPU: 명령어를 실행하는 부품이 1개만 존재

현재의 CPU: 명령어를 실행하는 부품이 여러개 존재

ex) 8 Core라면 CPU내에 명령어를 실행하는 부품이 8개 존재하는 것

코어를 여러 개 포함하는 CPU = 멀티 코어 CPU or 멀티코어 프로세서

*코어도 마찬가지로 개수가 많아진다고 CPU의 성능이 비례해서 증가하지 않음

스레드 and 멀티스레드

하드웨어적 스레드: 하나의 코어가 동시에 처리하는 명령어 단위

소프트웨어적 스레드: 하나의 프로그램에서 독립적으로 실행되는 단위

하나의 코어로 여러 명령어를 동시에 처리하는 CPU = 멀티 스레드 프로세서 or 멀티스레드 CPU

참고에서의 예시가 인상 깊어서 여기에 옮겨본다. '4코어 8(하드웨어스레드) 라는 것은, 상하권이 나뉜 4세트의 책과 같습니다. 이 4세트를 가지고 도서관에서 100명의 사람에게 빌려 줄 수 있습니다. 비록 한번에 읽을 수 있는 사람은 8 사람 (소프트웨어 스레드) 밖에 없지만요.'

https://juneyr.dev/thread

명령어 병렬 처리 기법

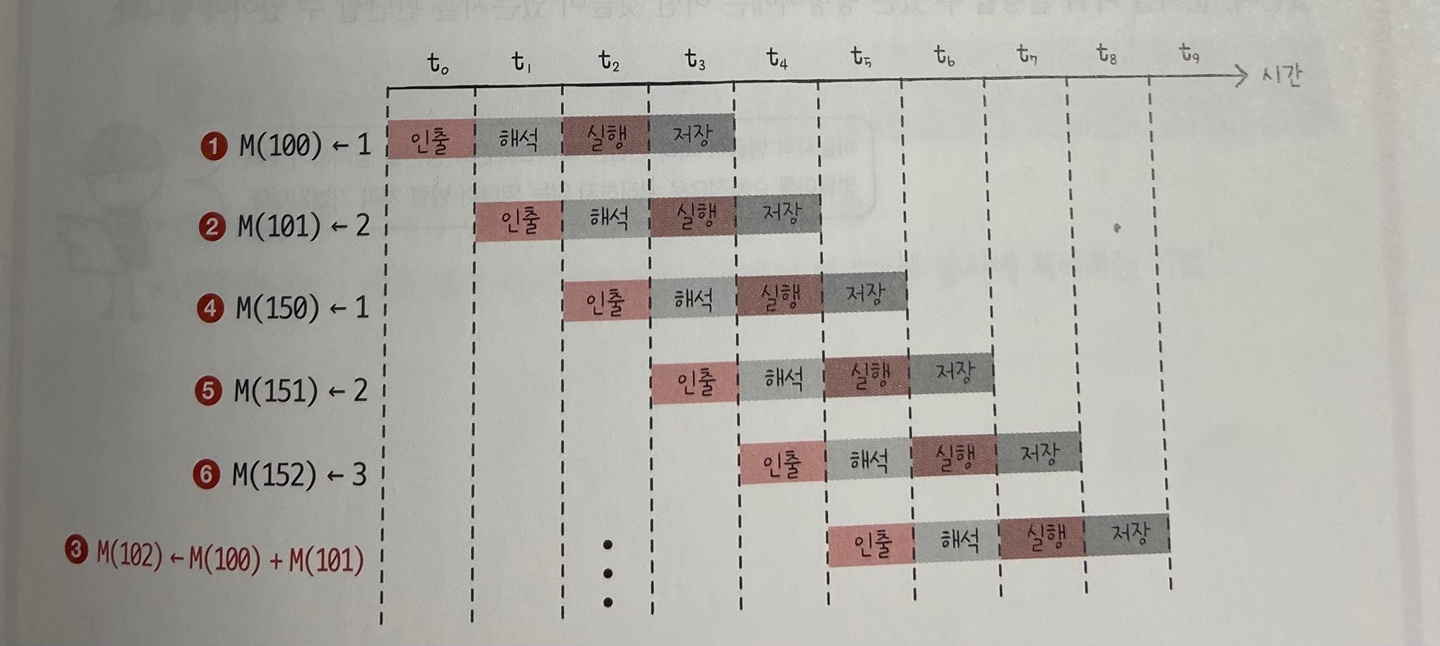

명령어 처리 과정

- 명령어 인출(fetch)

- 명령어 해석(decode)

- 명령어 실행(execute)

- 결과 저장(write back)

같은 단계가 겹치지만 않으면 CPU는 각 단계를 동시에 실행할 수 있음

ex) CPU가 한 명령어를 인출하는 동시에, 다른 명령어를 해석하고 또 다른 명령어를 실행하는 것이 가능함

이 사진에서 2단계를 보면 명령어1의 명령어 해석과 명령어2의 명령어 인출이 동시에 진행되고 있음

이 기법을 명령어 파이프라이닝이라고 함

파이프라인 위험

- 특정 상황에서의 실패

- 데이터 위험: 명령어 간 데이터 의존성으로 인해 발생,

- R1 = R2 + R3

- R4 = R1 + R5

- 위 상황에서 두 번째 명령은 R1의 값이 필요함, 첫 번째 명령어가 다 완료된 후 실행 가능

- 제어 위험: 분기로 인한 프로그램 카운터의 갑작스런 변화로 발생

- 제어 위험을 최소화하기 위해 분기 예측을 사용함

- 구조적 위험(자원 위험): 명령어를 겹쳐 실행하는 과정에서 서로 다른 명령어가 동시에 CPU 부품을 사용할 때 발생

슈퍼스칼라 파이프라인: CPU 내에 파이프라인을 여러 개 두어 명령어를 실행하는 것

비순차적 명령어 처리 기법(out of order executioin_OoOE): 순서를 바꿔 실행해도 무방한 명령어를 먼저 실행하여 명령어 파이프라인이 멈추는 것을 방지하는 기법

명령어 집합 구조(instruction set architecture_ISA): CPU가 이해할 수 있는 명령어 모음

ex) Intel CPU: x86 or x86-64 ISA, iphone: ARM ISA를 이해함

CISC(complex instruction set computer)

- 가변 길이 명령어

- 다양한 수의 명령어

- 상대적으로 적은 수의 명령어로 프로그램 실행이 가능함

RISC(reduced instruction set computer)

- 고정 길이 명령어

- CISC에 비해 명령어의 종류가 적음

- 자주 쓰이는 명령어만 사용

CISC는 메모리가 작은 시기에 인기가 높음 -> 작은 수의 명령어만으로 프로그램 동작이 가능

그러나 가변 길이 명령어로 인해 파이프라인을 구현하는 데 어려움이 존재함

RISC는 고정 길이 명령어로 CISC에 비해 파이프라인을 구현하는 것이 수월함

'Computer > CS' 카테고리의 다른 글

| blocking and nonblocking / Synchronous and Asynchronous (0) | 2023.01.08 |

|---|---|

| 컴퓨터 구조(6) - 메모리와 캐시 메모리 (0) | 2022.11.15 |

| 컴퓨터 구조(4) - CPU (0) | 2022.11.13 |

| 컴퓨터 구조(3) - 명령어 (0) | 2022.11.12 |

| 컴퓨터 구조(2) - 정보 단위 (0) | 2022.11.12 |